Microlise ML10 ML10 Tracking Unit User Manual Product Data Sheet

Microlise Limited ML10 Tracking Unit Product Data Sheet

Contents

- 1. QOQWT32I Module - User Manual

- 2. User Manual

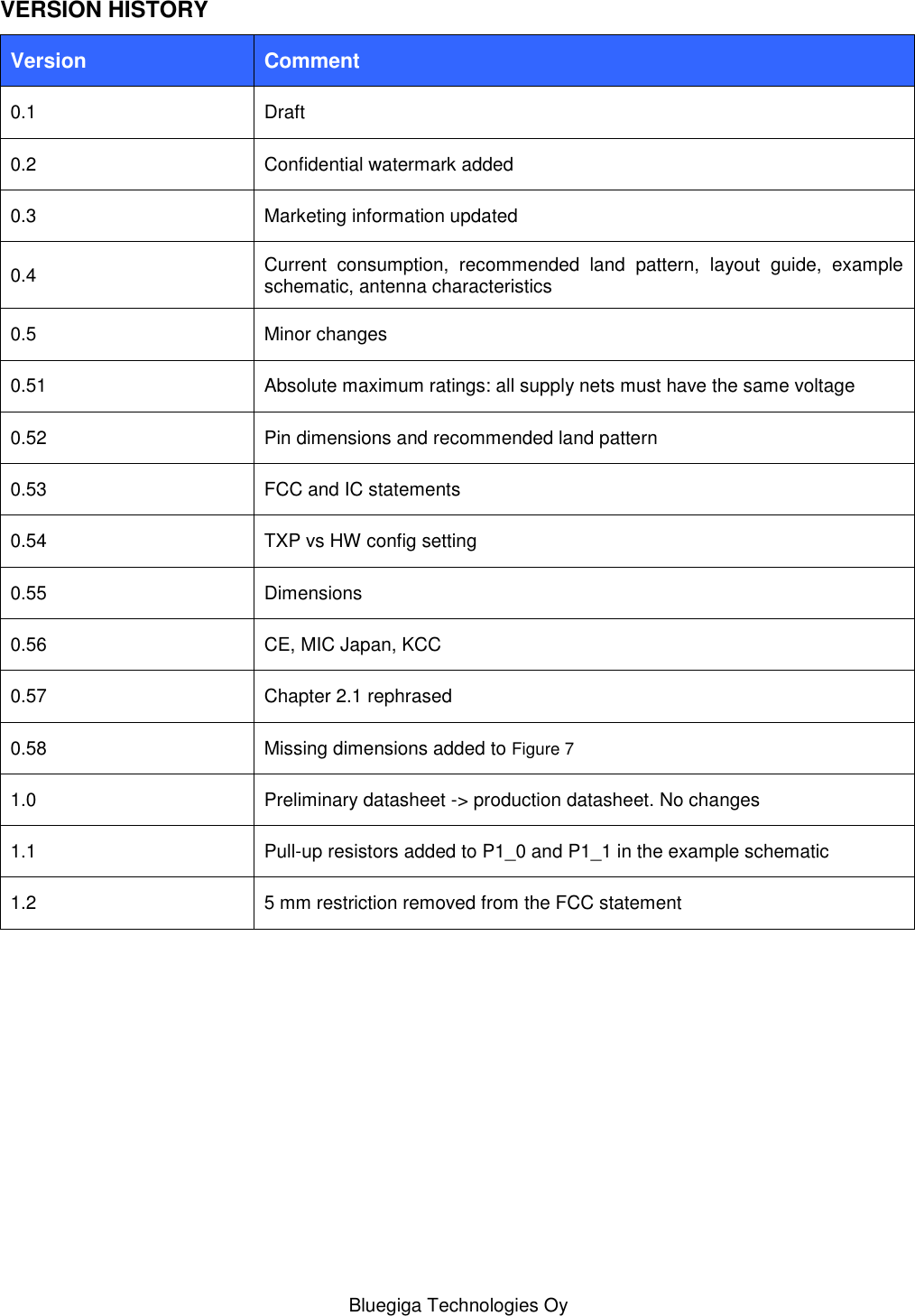

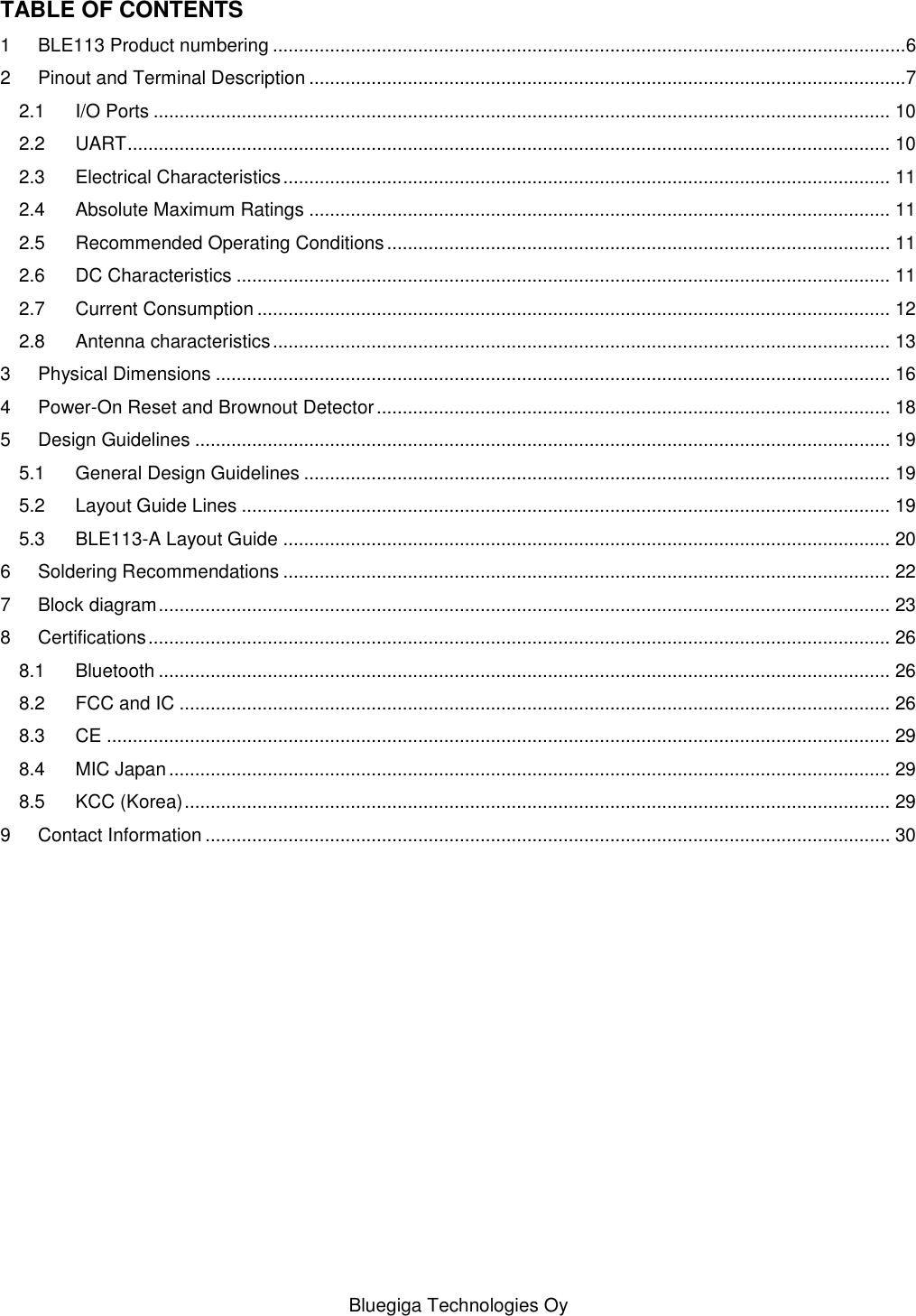

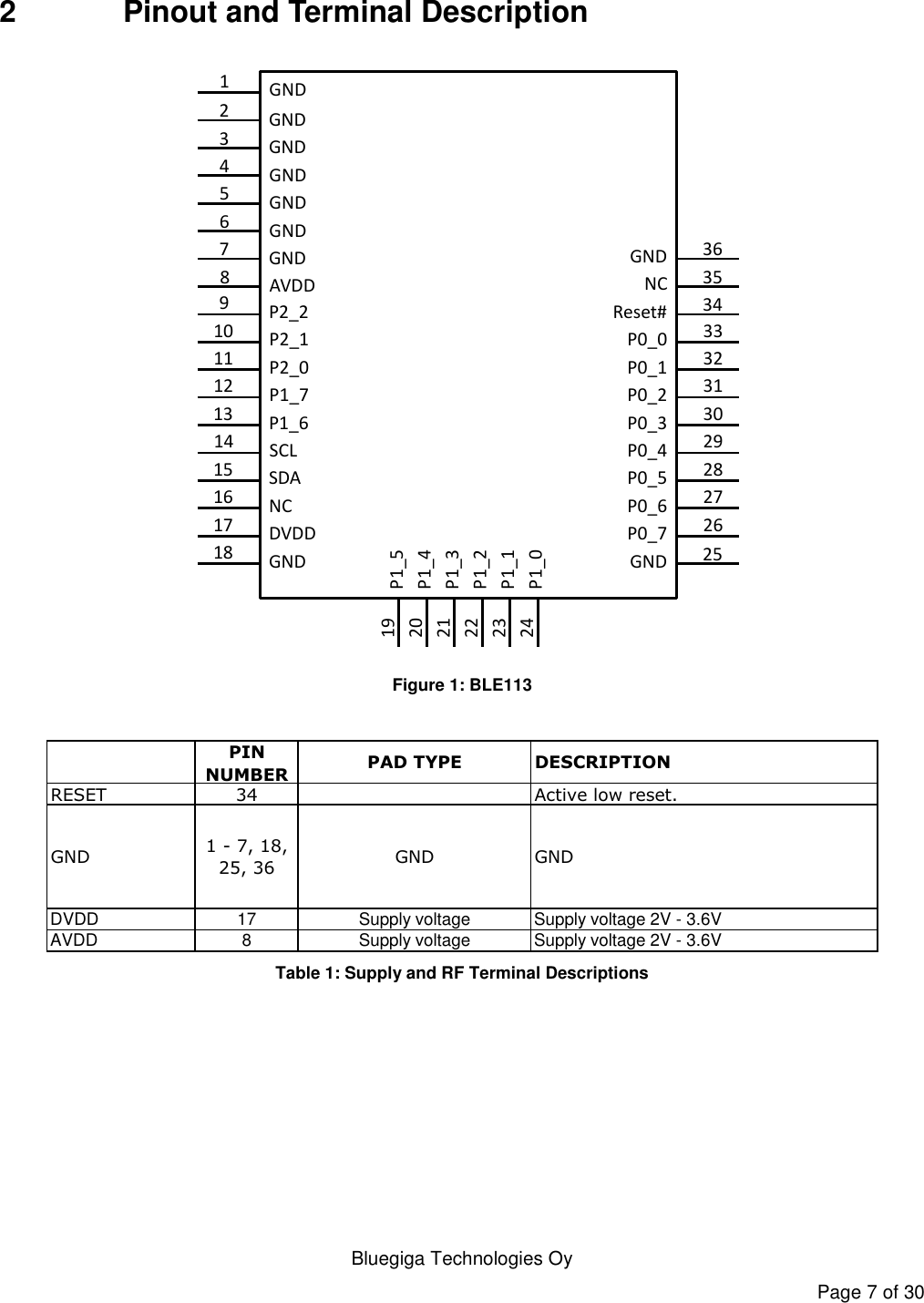

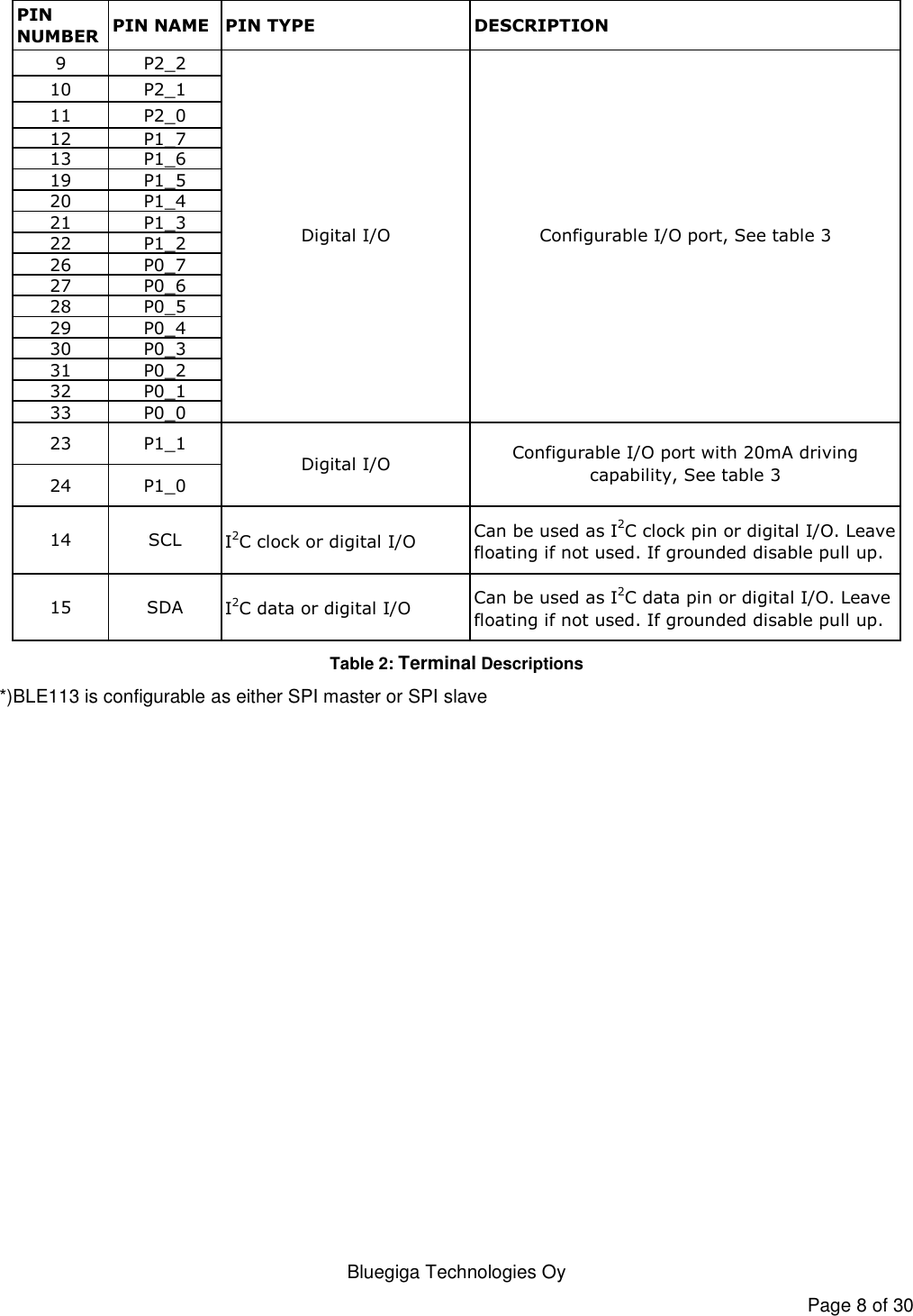

- 3. QOQBLE113 Module - User Manual

- 4. QIPEHS6 Module - User Manual

QOQBLE113 Module - User Manual